A hybrid pixel detector with a pixel readout application-specific integrated circuit (ASIC) connected to a pixel radiation sensor by the flip-chip method is the common solution for space-borne X-ray imaging applications. It will have different degrees of voltage drop among the pixel element with the growing of pixel array size. Therefore, improving the consistency of the measured data from each pixel readout circuit is critical for the development of such pixel readout ASIC. The inconsistent power supply voltages between pixel elements should be improved in the real applications.

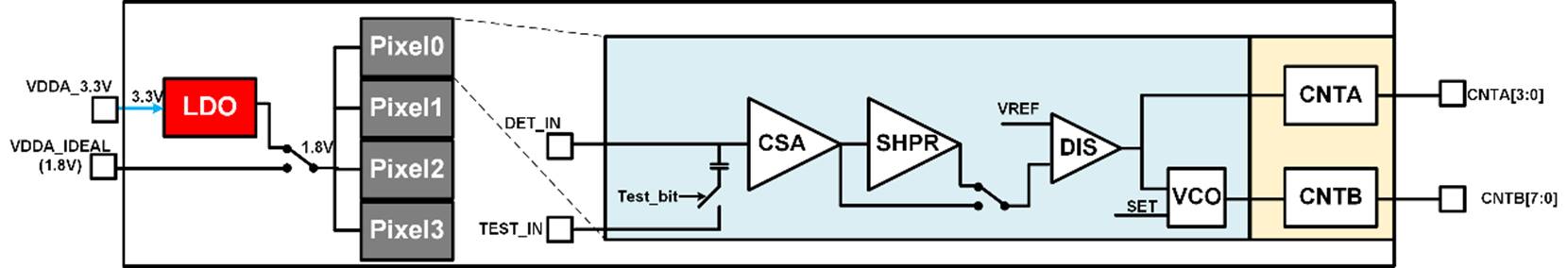

Fig.1 The schematic of a built-in LDO super pixel element.

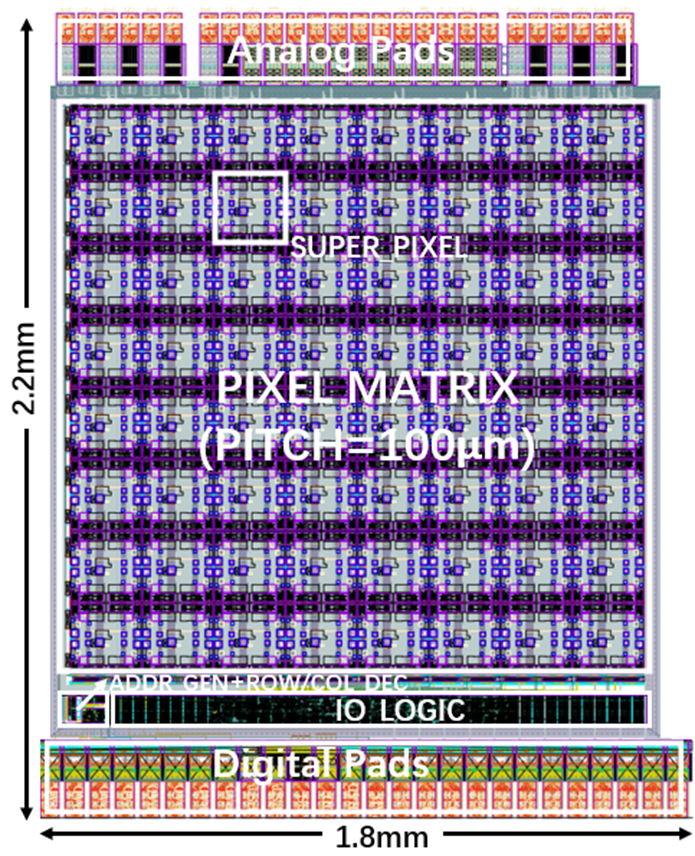

In our group, a novel pixel circuit topology with a built-in low-dropout (LDO) regulator to enhance consistency in an energy-resolving photon-count pixel readout ASIC was presented. The ASIC prototype including a 16×16 pixel matrix and peripheral digital readout circuits is designed in CMOS 0.18 μm mixed-signal 3.3 V and 1.8 V process. Each pixel analog front-end circuit includes a charge-sensitive amplifier (CSA), a CR-RC pulse shaper, two discriminators with different threshold voltage signals, a 4-bit counter for photon counting, and an 8-bit counter for TOT energy measurement. A common LDO regulator is built into the super pixel to provide stable supply voltage signals for analog blocks of four pixels, ensuring the consistency of each pixel unit for large scale arrays. The digital part of this ASIC mainly includes an IO logic, address generators, row, column decoders and a I2C controller. The die size is 1.8 mm × 2.2 mm. The layout is shown in Fig.2.

Fig.2 Layout of the fabricated chip

The simulation results are obtained. The input charge range is 1 ~ 10 fC. The CSA capacitance setting the input stage gain to 36 mV/fC. The equivalent noise charge (ENC) is 200 e- @ 200 pF. The simulated gain and ENC between pixels are homogeneous. The power dissipation is about 40 μW/pixel.

For future work, the ASIC will be tested for performance evaluation. Moreover, the consistency of the measured data from each pixel readout circuit will be improved to satisfy the requirements of large-scale pixel matrix for X-ray imaging applications.

(Authors: J. Cheng, Reviewer: W. Gao)