In our group, we have developed a current-mode photon-counting readout ASIC for high-gain detectors to meet this target. A prototype of the proposed front-end ASIC (named as SENSROC 14) is designed and implemented in 0.35 μm 3.3V CMOS technology. In this chip, eight readout channels, two dummy channels, bias circuits, and I2C interface circuits. The chip size is 2.4 mm x 2.6 mm.

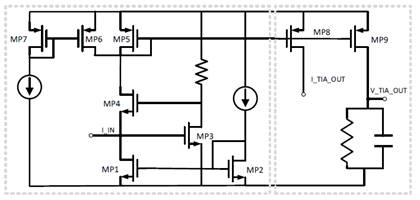

A regulated common-gate amplifier and a current-mirror current mirror with negative feedback are proposed to implement the preamplifiers. The input resistance and the -3dB bandwidth of these preamplifiers are carefully taken into account. In addition, a current-mode comparator is adopted to reduce the propagation time. In order to mitigate the effects of preamplifier output noise, a current-mode comparator with hysteresis is designed.

The maximum input charge is 100 pC. The minimum input impedance and the maximum -3dB bandwidth of the preamplifier are 20 Ω and 600 MHz, respectively. The maximum propagation time of the current comparator is less than 5 ns. The counting rate exceeds 10 Mcps. The fabricated chip has been back. The die photograph is given.

The performance of the proposed circuits will be evaluated in the next step.

(Authors: J. W. Wang, Reviewer: W. Gao)