Introduction

A radiation-hardened mixed-signal microcontroller system-on-chip (SoC) is required to construct a on-board computer built in fully-customized nanosatellites for space applications.

Architecture of the MCU

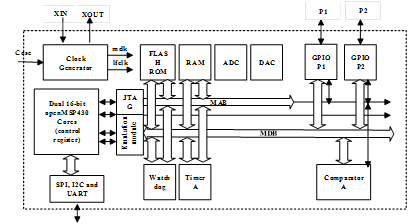

In our proposed microcontroller, the processor design is based on open-source processor named openMSP430. The open source MSP430 core is a 16-bit RISC low-power processor that implements all the instruction sets of an MSP430x1xx family of MCUs. In order to enhance the reliability, a dual-modular redundant processor has been designed. The SRAM is mainly composed of storage arrays and peripheral circuits. The basic memory cell unit uses the 6T structure and optimizes the layout using the method in paper. To meet the above design requirements, an eight channels, 12bit, 2MS/s ADC is designe, and a 12-bit, 10MS/s DAC is designed. To provide the clock for all SoC modules, a 32/16/8/1MHz clock generator is designed. To complete the communication function, the I2C, SPI and UART interface buses are designed. Wi-Fi, ZigBee and S-Band communication modules can link to these buses.

Figure 1 The architecture of the proposed microcontroller SoC

Prototype chips and Experimental results

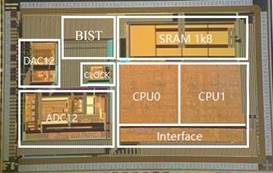

The radiation-hardened microcontroller SoC is implemented with the 180nm CMOS process, named MSuC430V2. The microcontroller SoC’s micrograph is shown in Fig. 2. The 16-bit dual-modular redundant processor is located on the right side of the chip, the 1 kB SRAM memory is located at the top right of the chip, the ADC is located at the bottom left of the chip, the DAC is located at the left side of the chip, the clock generation is located at the center of the chip. The proposed SoC area of 5mm × 3mm. In order to test the function of the SoC, a customized mother-daughter PCB board is designed.

Figure 2 The micrograph of the proposed SoC

The performance evaluation results are shown in Table 1. The proposed microcontroller SoC, namely MSuC430V2, could satisfy the requirements of satellites for ADR.

Table 1 Main specifications of the propsed SoC

Parameter |

performance index |

Process |

TSMC 0.18μm,1.8/3.3V |

Dynamic Power |

1.9mW / MHz |

Area |

4.5mm×5mm |

CPU |

16bits, 32MHz, 0.404 DMIPS/MHz |

SRAM |

8kB, 6T, Period of memory access 30ns |

ADC12 |

12bit,2MS/s, 10mW, 8 channel input |

DAC12 |

12bit, 10MS/s,4mW |

Oscillator |

100KHz,1MHz,1MHz, Jitter 1.41ns |

PLL |

32/16/8/1MHz, Jitter 718ps |

For more information, please readout the following paper.

2019_MEJ_X.Ge_W.Gao.pdf

2019_MEJ_X.Ge_W.Gao.pdf